# **Trusted Computations in Vehicular Environments**

# **Marc Lacoste**

Orange Innovation

Journées Sécurité, October 14-15, 2021

# **Outline**

- (Beyond) 5G vehicular isolation & trust

- The TEE approach

- TEE architectures

- Intel SGX and other TEEs

- Isolation and resilience framework for V2X

- New directions

- Confidential computing

- Decentralized protocols

- Integration with ML

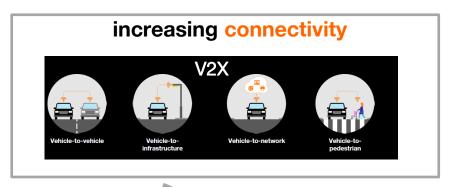

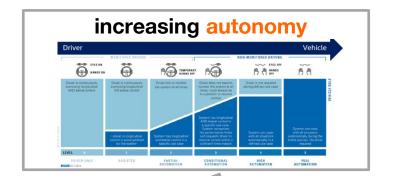

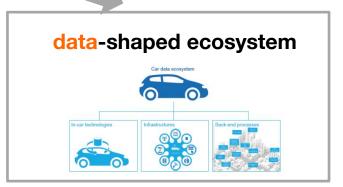

# connected & autonomous vehicles: security, safety & privacy concerns

increasing complexity

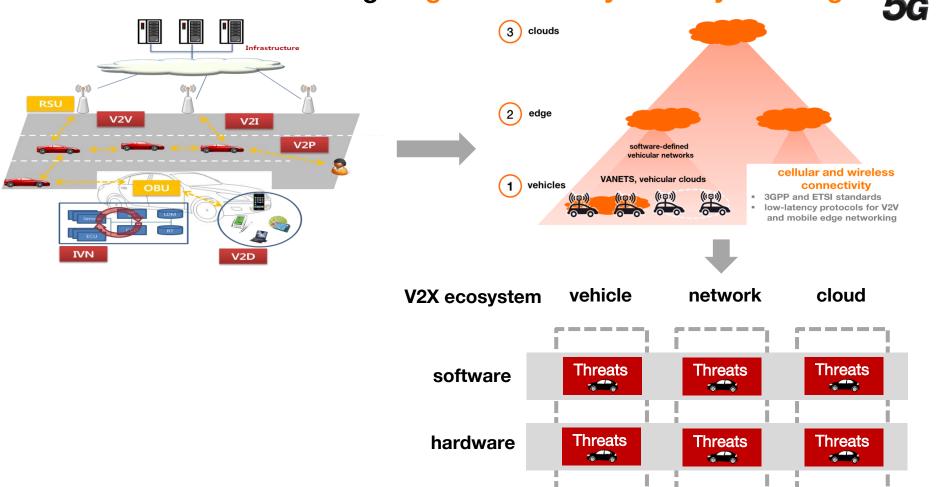

# **B5G** vehicular networking magnifies security & safety challenges

# **B5G** vehicular networking magnifies security & safety challenges

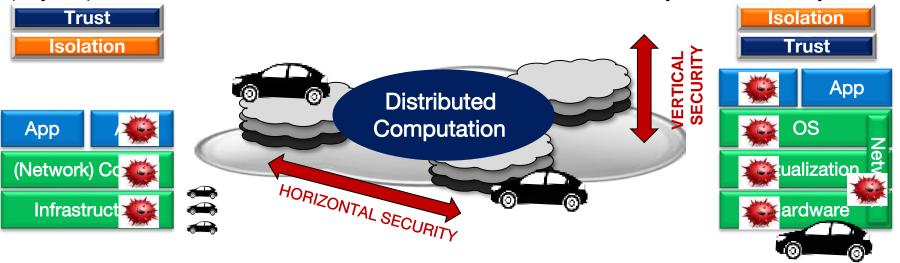

# isolation : which place for protection mechanisms in a multi-tier ecosystem?

- network connections

- multi-tenancy

- system-to-network, end-to-end

# how to guarantee data protection?

- confidentiality and privacy

- authenticity and integrity of information sources

- relation with safety

# a holistic vision of protection is needed:

- software and hardware

- for vehicle, network, and cloud tiers

- covering the full data life-cycle

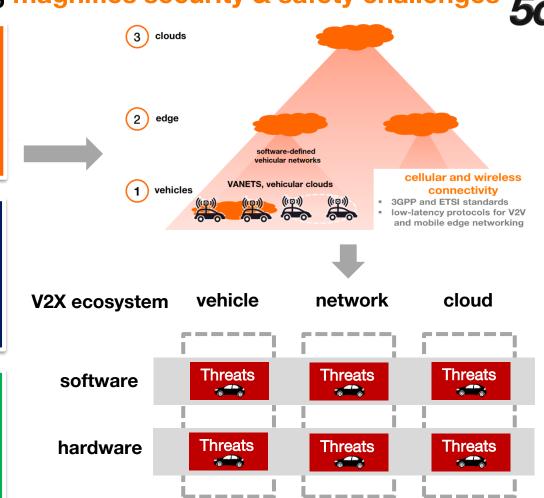

# **B5G** vehicular networking magnifies security & safety challenges

# isolation : which place for protection mechanisms in a multi-tier ecosystem?

- network connections

- multi-tenancy

- system-to-network, end-to-end

# how to guarantee data protection?

- confidentiality and privacy

- authenticity and integrity of information sources

- relation with safety

# a holistic vision of protection is needed:

- software and hardware

- for vehicle, network, and cloud tiers

- covering the full data life-cycle

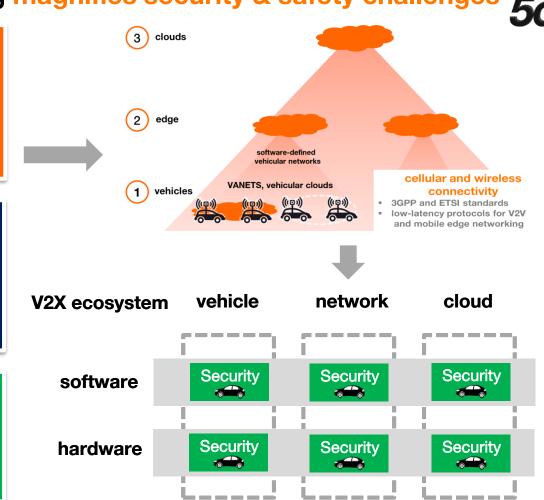

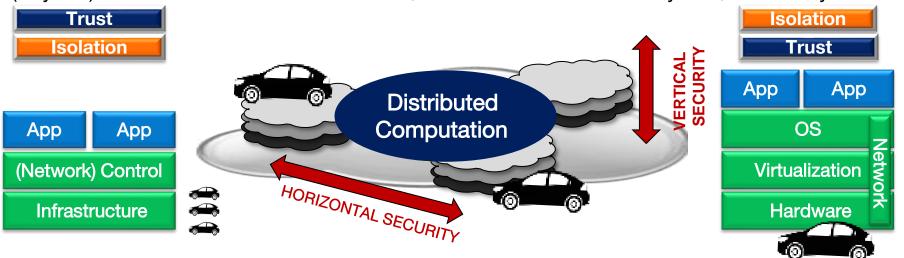

# problem statement revisited

(Beyond) 5G infrastructures are virtualized, multi-domain and multi-layered, with many threats

# problem statement revisited

(Beyond) 5G infrastructures are virtualized, multi-domain and multi-layered, with many threats

# problem statement revisited

(Beyond) 5G infrastructures are virtualized, multi-domain and multi-layered, with many threats

how to perform (distributed) computations securely over untrusted B5G vehicular infrastructures?

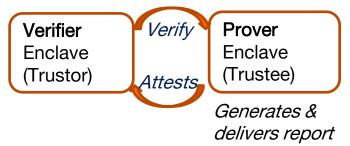

# security properties and primitives

#### PROTECTING THE INFRASTRUCTURE

Attestation Framework

Isolation **Framework**

**Program** Sandboxing

Confine untrusted programs Protect system from their actions

**Platform Attestation**  Guarantee that the platform runs trustworthy hardware, firmware, and software before transferring computation and data

#### PROTECTING COMPUTATIONS

Isolated **Execution**  Protect code from the rest of the system

**Isolated compartments**

- **❖ CREATE / DESTROY**

- **❖ ENTER / EXIT**

#### **Confidentiality:**

- "Black box" execution of programs

- Secure communication of data with untrusted outside world

Secure load and store data

Secure LOAD / STORE

**Privacy:** Private Tamper-Evident EE

Integrity:

The system cannot affect the behavior of programs that run as on reference platform

**Attestation** Proof of correct execution

ATTEST / VERIFY

**Shielded Execution**

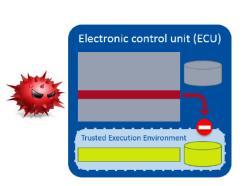

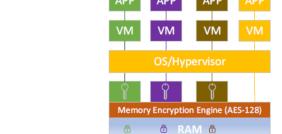

#### evolutions of in-vehicle architecture

in-vehicle HW architecture is increasingly virtualized, raising isolation concerns

#### **Hardware ECUs**

Source: Wasicek et al. Context-aware Intrusion Detection in Automotive Control Systems. ESCAR Conference, 2017.

- Safety-critical vehicle functions connected by vulnerable HW bus

- Cyber-resilience: propagation of failures and attacks through vulnerable gateway

- Challenges:

- ECU protection

- In-vehicle network protection

- Gateway protection

#### **Domain-based ECUs**

Source: NXP.

- ECUs grouped into domains for broad functional areas

- ECU domains isolated / monitored by Domain Controllers

- Challenges:

- Inter-domain isolation

- Trade-offs

#### **Virtualized ECUs**

Source: NXP.

- ECUs as virtualized execution environments (e.g., VMs, containers)

- Distributed computations across ECUs / vehicles

- Challenges:

- EE isolation

- Untrusted EE platform

- Side-channels

⇒ hardware trusted execution execution technologies

# **Outline**

- (Beyond) 5G vehicular isolation & trust

- The TEE approach

- TEE architectures

- Intel SGX and other TEEs

- Isolation and resilience framework for V2X

- New directions

- Confidential computing

- Decentralized protocols

- Integration with ML

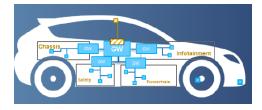

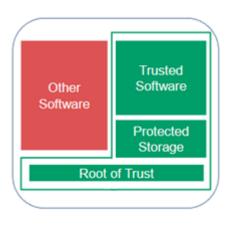

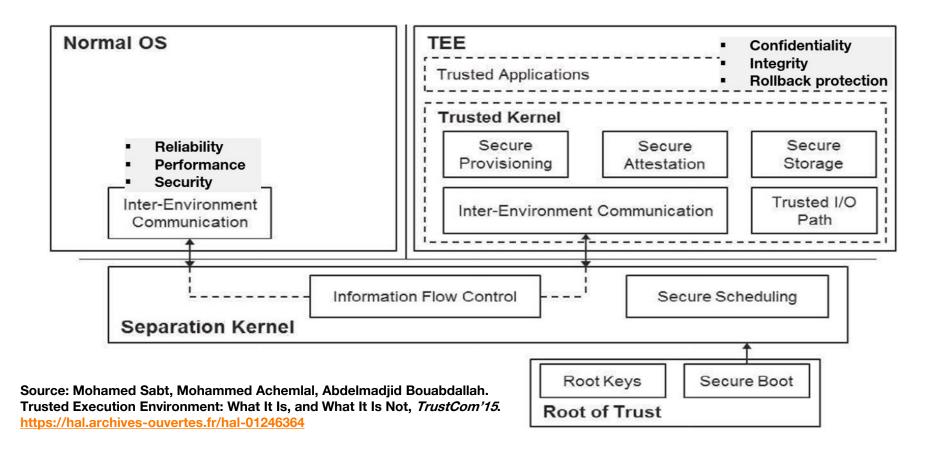

#### **Trusted Execution Environment**

# hardware support to run arbitrary code in a confined environment : guarantees tamper-resistant execution of applications

- isolated execution

- tamper-resistant storage: sealing create, store, and manage secrets in a controlled environment

- reporting to a remote verifier: attestation extend trust to internal and external entities

- secure provisioning

- trusted path

Trusted Platform Modules

Intel Software Guard Extensions

# **TEE** guarantees isolation + trust

#### Isolation

## protected compartment concept

Source: Jens Köhler and Henry Förster. Trusted Execution Environments in Vehicles for Secure Driver Assistance Systems, 2017, Springer.

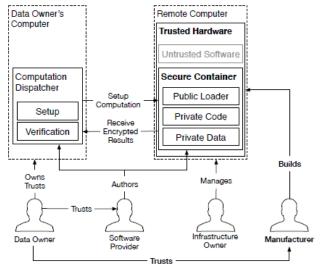

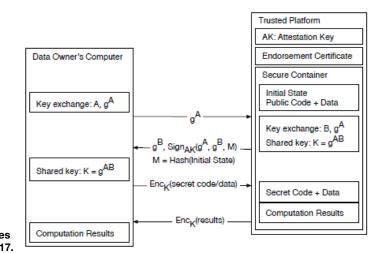

#### Trust

## secure remote computation

- prove to remote party it is talking to software located in secure container hosted on trusted hardware

- attestation key

- endorsement certificate

- security-sensitive state (code + data) in TEE cannot be corrupted from outside of TEE

- trusted hardware protects integrity and confidentiality of computations

- multiple concurrent compartments

Source: V. Costan, I. Lebedev and S. Devadas. Secure Processors Part I: Background, Taxonomy for Secure Enclaves and Intel SGX Architecture. Foundations and Trends in Electronic Design Automation, vol. 11, no. 1-2, pp. 1–248, 2017.

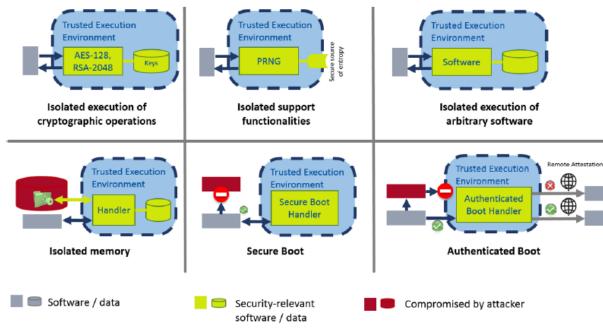

#### **TEE** features

#### isolation

- access control to code and data

- well-defined entry point

- concurrent modules

#### attestation

- prove to third party attested state

- locally or remotely

- measurement during init

#### sealing

- confidential data

can be unwrapped

under some conditions

- encryption

Source: J. Köhler and H. Förster. Trusted execution environments in vehicles for secure driver assistance systems, 2017, Springer.

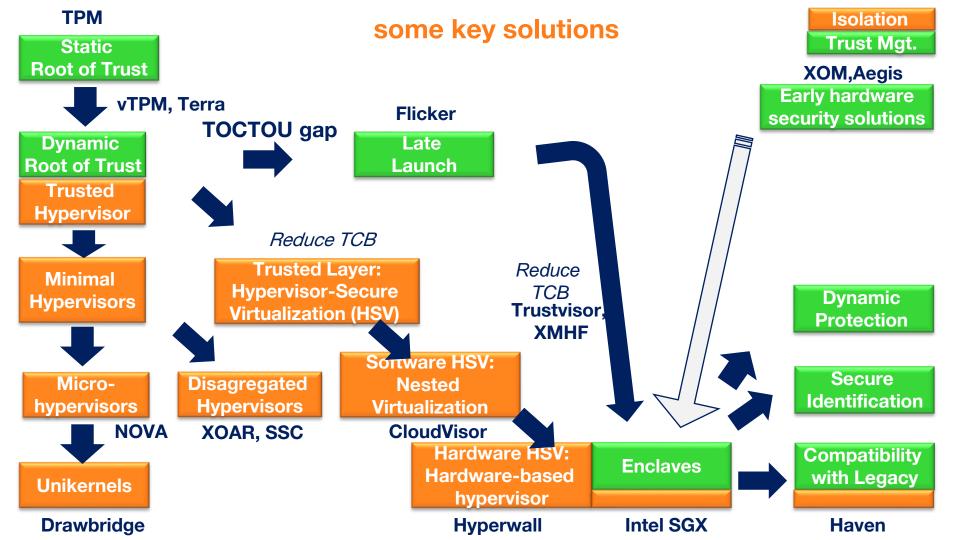

#### **DRoT**

- trust chains

- TOCTOU vulnerabilities

- code and data confidentiality

- side-channel resistance

- memory protection

#### **TEE** architecture

# key challenges

#### isolation

- attack surface:

- TCB size

- hardware or software TCB?

- side-channel attacks, exceptions

- flexibility:

- dynamic/upgradeable protected space

- concurrent compartments

- compartment size limitations

#### attestation

- secure proofs

- large code size

- low overhead:

- secure element resource usage

- communication

- proof verification

# compatibility with legacy

- unmodified binaries support

- on-chip or co-processor?

- independence from hardware

- easy access to specifications

- amount of trust in provider

Source: https://semiengineering.com/dodging-the-next-generation-of-car-thieves/

# **Outline**

- (Beyond) 5G vehicular isolation & trust

- The TEE approach

- TEE architectures

- Intel SGX and other TEEs

- Isolation and resilience framework for V2X

- New directions

- Confidential computing

- Decentralized protocols

- Integration with ML

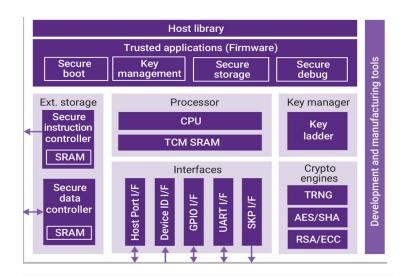

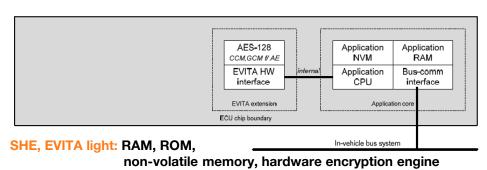

# for V2X

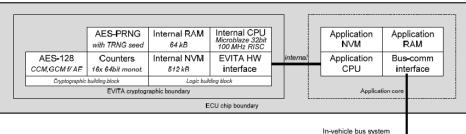

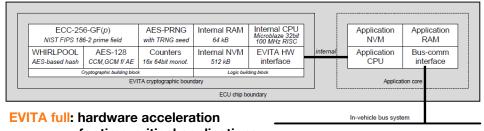

#### **HSM**

- hardware module runs software components isolated from other software components

- SoC, external module, Integrated Circuit

- examples:

- Secure Hardware Extension (SHE), EVITA HSM

- TPM

- Smart cards (eSIM)

#### **CPU** security extensions

- realms / enclaves isolated by the hardware

- examples:

- Intel TXT

- ARM Trustzone

- Intel SGX

#### virtualization solutions

virtualization (full or lightweight) guarantees isolation examples: hypervisors (Xen, KVM) containers (LXC) unikernels Source: EVITA project

**EVITA medium:** secure CPU (aymmetric crypto)

for time-critical applications

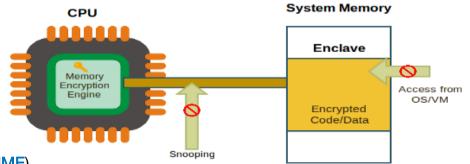

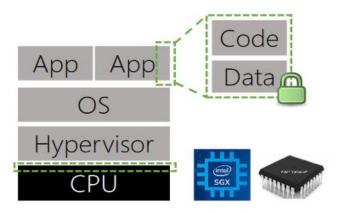

## Intel SGX

#### Enclave: secure run-time environment isolated from external access

# **Memory protection**

- Only CPU is trusted

- Multi-threaded execution

- New hardware instructions

- Enclave creation (ECREATE)

- Adding pages (EADD), sealing

- Enclave mode call gate (EENTER, EEXIT, ERESUME)

- Enclave Page Cache (EPC):

Physical memory region to store pages, transparently encrypted, integrity–protected

- SGXv2:

Dynamic memory allocation, EPC permission change

#### **Attestation**

- CPU-based attestation:

- On-demand generation of reports (EREPORT)

- Verification of report integrity

- Quoting enclave for remote attestation

Verifies report integrity includes in CoT

# **ARM Trustzone, AMD SEV**

Co-processor Secure World (TEE) Normal World (REE) DRAM user mode: user mode: App TEE App kernel mode: kernel mode: OS TEE-kernel hyp mode: Hypervisor APB smc smc monitor mode: Secure Monitor Mode Secure world Normal world

CPU Core

- partition of resources in two worlds:

- Normal world

- Secure World

- Secure Monitor between worlds

Source: Zhichao Hua, Jinyu Gu, Yubin Xia, Haibo Chen, Binyu Zang, Haibing Guan. vTZ: Virtualizing ARM TrustZone, *USENIX Security Symposium*, 2017.

encryption of VM memory image confidentiality but not integrity protection

**AMD SEV**

**ARM TrustZone**

# comparisons

|                             |     |              |             |              |      |       |          |                                        | ancel |       |               |                      |       |                   |                      |            | .3     | ility |                                     |

|-----------------------------|-----|--------------|-------------|--------------|------|-------|----------|----------------------------------------|-------|-------|---------------|----------------------|-------|-------------------|----------------------|------------|--------|-------|-------------------------------------|

|                             | 150 | olatio<br>At | n<br>testat | ion<br>aling | nami | ic Ro | de Memor | alityesist<br>el Protect<br>cy Protect | ion   | intwi | ight<br>Proce | essor<br>N-On<br>Pri | ly To | B<br>tion<br>nami | e Layout<br>Bradeabl | e TCB Corr | iPati. | en-S  | ource<br>ademic 15A<br>a Target 15A |

| AEGIS [46]                  | •   | •            | •           | •            | •    | 0     | •        |                                        | 0     | 0     | •             | •                    | •     | 0                 | •                    |            | 0      | •     | _                                   |

| TPM [47]<br>TXT [22]        | 0   | •            | •           | 0            | •    | -     | 0        |                                        | 0     | •     | •             | -0                   | -     | 00                | •                    |            | 00     | 0     | x86_64                              |

| TrustZone [1]               | •   | 0            | 0           | •            | 0    | 0     | 0        |                                        | 0     | 0     | •             | •                    | •     | 0                 | •                    |            | 0      | 0     | ARM                                 |

| Bastion [9]                 | •   | 0            | •           | •            | •    | 0     | •        |                                        | 0     | 0     | 0             | •                    | •     | •                 | •                    |            | 0      | •     | UltraSPARC                          |

| SMART [14]                  | 0   | •            | 0           | •            | 0    | 0     | 0        |                                        | •     | 0     | 0             | _                    | -     | 0                 | •                    |            | 0      | •     | AVR/MSP430                          |

| Sancus [39]<br>Soteria [21] | •   | •            | 00          | •            | 0    | 00    | 0        |                                        | •     | 0     | •             | 00                   | 0     | 00                | 0                    |            | •      | •     | MSP430<br>MSP430                    |

| SecureBlue++ [49]           | •   | 0            | •           | •            | •    | 0     | •        |                                        | 0     | 0     | •             | •                    | •     | 0                 | •                    |            | 0      | 0     | POWER                               |

| SGX [35]                    | •   | •            | •           | •            | •    | 0     | •        |                                        | 0     | 0     | 0             | •                    | •     | •                 | •                    |            | 0      | 0     | x86_64                              |

| Iso-X [15]                  | •   | •            | 0           | •            | 0    | 0     | •        |                                        | 0     | 0     | 0             | •                    | •     | •                 | •                    |            | 0      | •     | OpenRISC                            |

| TrustLite [28]              | •   | •            | 0           | 0            | 0    | 0     | 0        |                                        | •     | 0     | 0             | •                    | •     | •                 | •                    |            | 0      | •     | Siskiyou Peak                       |

| TyTAN [8]                   | •   | •            | •           | •            | 0    | 0     | 0        |                                        | •     | 0     | 0             | •                    | •     | •                 | •                    |            | 0      | •     | Siskiyou Peak                       |

| Sanctum [12]                | •   | •            | •           | •            | •    | •     | 0        |                                        | 0     | 0     | 0             | •                    | •     | •                 | •                    |            | •      | •     | RISC-V                              |

$<sup>\</sup>bullet$  = Yes;  $\bullet$  = Partial;  $\bigcirc$  = No;  $\bullet$  = Not Applicable

Source: P. Maene, J. Götzfried, R. de Clercq, T. Müller, F. Freiling and I. Verbauwhede. Hardware-Based Trusted Computing Architectures for Isolation and Attestation. *IEEE Transactions on Computers*, vol. 67, no. 3, pp. 361-374, March 2018.

<sup>&</sup>lt;sup>1</sup>Resistance against software side-channel attacks targeting memory access patterns only.

<sup>&</sup>lt;sup>2</sup>Protection from physical attacks, both passive (e.g., probing) and active (e.g., fault injection).

# comparisons

Source: J. Köhler and H. Förster. Trusted Execution Environments in Vehicles for Secure Driver Assistance Systems, 2017.

|                               | Functionality                                  |                               |                                |                               |                                                  |                                |                                                     |                     |                                          |                 |             |                    | Security properties                 |                              |                                  |                    |                                         |                            |                                      |                            | Cost                    |                  |                                                           |  |

|-------------------------------|------------------------------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------------------------------------|--------------------------------|-----------------------------------------------------|---------------------|------------------------------------------|-----------------|-------------|--------------------|-------------------------------------|------------------------------|----------------------------------|--------------------|-----------------------------------------|----------------------------|--------------------------------------|----------------------------|-------------------------|------------------|-----------------------------------------------------------|--|

|                               | Isolated execution of cryptographic operations | - Symmetric cryptography (SW) | - Asymmetric cryptography (SW) | - Symmetric cryptography (HW) | <ul> <li>Asymmetric cryptography (HW)</li> </ul> | Isolated support functionality | <ul> <li>RNG with secured entropy source</li> </ul> | - Monotonic counter | Isolated execution of arbitrary software | Isolated memory | Secure Boot | Authenticated Boot | Protection against physical attacks | - High degree of integration | - Side-channel attack resistance | - Hardware binding | Protection against non-physical attacks | - TCB realized in hardware | - TCB realized in hard- and software | - TCB realized in software | Relative financial cost | Prevalent design | Updateability of the software that is executed in the TEE |  |

| Hardware Security Modules     |                                                |                               |                                |                               |                                                  |                                | .7                                                  | -                   |                                          |                 |             |                    | Marriel                             | 3/1                          |                                  | 300.00             |                                         |                            |                                      | 20                         |                         |                  |                                                           |  |

| – SHE [4]                     |                                                |                               |                                | Х                             |                                                  |                                | X                                                   |                     |                                          | (x)             | X           |                    |                                     | Χ                            | (x)                              | Х                  |                                         | X                          |                                      |                            | low                     | SoC / IC         | none                                                      |  |

| - EVITA light [5]             |                                                |                               |                                | X                             |                                                  |                                | X                                                   |                     | _                                        | (x)             | (x)         | (x)                |                                     | X                            | (x)                              | x                  |                                         | X                          | _                                    |                            | low                     | SoC / IC         | none                                                      |  |

| - EVITA medium [5]            |                                                | X                             | X                              | X                             |                                                  |                                | X                                                   | X                   |                                          | Х               | X           | X                  |                                     | X                            | (x)                              | х                  |                                         | ×                          |                                      |                            | low                     | SoC / IC         | (SW Update)                                               |  |

| – EVITA full [5]              |                                                | Х                             | X                              | Х                             | х                                                |                                | X                                                   | Х                   |                                          | Х               | Х           | х                  |                                     | Х                            | (x)                              | х                  |                                         | X                          |                                      |                            | medium                  | SoC / IC         | (SW Update)                                               |  |

| – TPM 1.2 [6]                 |                                                |                               |                                | X                             | X                                                |                                | X                                                   | Х                   |                                          | X               | х           | X                  | 8 - 8                               |                              | (x)                              | (x)                |                                         | ×                          |                                      |                            | high                    | EM               | none                                                      |  |

| – TPM 2.0 [7]                 | _                                              | (x)                           | (x)                            | Х                             | х                                                |                                | Х                                                   | Х                   | _                                        | х               | х           | ×                  | _                                   | _                            | (x)                              | (x)                |                                         | ×                          | _                                    |                            | high                    | EM               | none                                                      |  |

| - Smartcard [8]               | _                                              | (x)                           | (x)                            | _                             |                                                  |                                | X                                                   |                     | _                                        | Х               |             | _                  |                                     | _                            | (x)                              | (x)                |                                         | X                          |                                      |                            | low                     | EM               | (SW Update)                                               |  |

| CPU security extensions       |                                                |                               |                                |                               |                                                  |                                |                                                     |                     |                                          |                 |             |                    |                                     |                              |                                  |                    |                                         |                            |                                      |                            |                         |                  |                                                           |  |

| - ARM TrustZone [9]           |                                                | Х                             | X                              | (x)                           | (x)                                              |                                | Х                                                   | Х                   | Х                                        | Х               | Х           | X                  |                                     | (x)                          | (x)                              | (x)                | Т                                       |                            | Х                                    | low-                       | SoC                     | (SW Update)      |                                                           |  |

| - Intel TXT [10]              | _                                              | X                             | X                              | (x)                           | (x)                                              |                                | X                                                   | Х                   | X                                        | Х               | Х           | х                  | _                                   | (x)                          | (x)                              | (x)                | _                                       | _                          | Х                                    |                            | high                    | SoC              | (SW Update)                                               |  |

| Virtualization solutions      |                                                |                               |                                |                               |                                                  |                                |                                                     |                     |                                          |                 |             |                    |                                     |                              |                                  |                    |                                         |                            |                                      |                            |                         |                  |                                                           |  |

| - Hypervisor (e.g., Xen [11]) |                                                | х                             | Х                              |                               |                                                  |                                | (x)                                                 |                     | Х                                        | Х               | (x)         | (x)                |                                     |                              |                                  |                    |                                         |                            |                                      | Х                          | low-                    | Software         | SW Update                                                 |  |

| - Container (e.g., LXC [13])  |                                                | X                             | X                              |                               |                                                  |                                | (x)                                                 |                     | X                                        | х               |             |                    | _                                   | _                            | _                                | _                  |                                         | _                          | _                                    | X                          | high                    | Software         | SW Update                                                 |  |

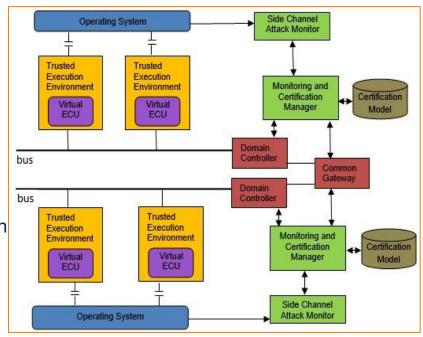

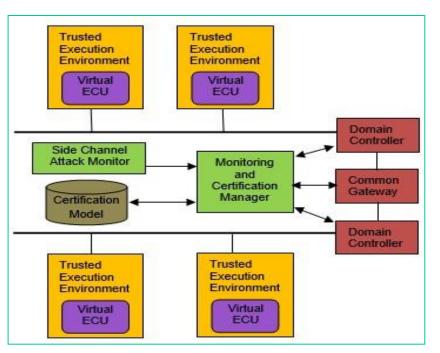

#### V2X isolation and resilience

- ECUs as virtualized execution environments

- distributed computations

goals: framework for isolation and resilience for next-generation critical vehicular functions (ECUs)

#### challenges:

- ECU isolation : trusted execution

- resilience : certificate-based anomaly detection

- side-channels : hardware performance counters

- interoperability : AUTOSAR framework

#### results:

- survey: vehicular isolation architecture, threats, mitigation

- isolation & resilience framework : FFIVR with PoC [VEHICULAR 2020]

# FIIVIR: a Framework for Improving In-Vehicle Isolation and Resilience

Trusted Execution Environment (TEE)

secure isolated execution environments for FCUs

Monitoring and Certification Manager (MCM) real-time anomaly detection of in-vehicle network

Side Channel Attack Monitor run-time detection of side-channel attacks

# **Outline**

- (Beyond) 5G vehicular isolation & trust

- The TEE approach

- TEE architectures

- Intel SGX and other TEEs

- Isolation and resilience framework for V2X

- New directions

- Confidential computing

- Decentralized protocols

- Integration with ML

# multi-dimensional heterogeneity challenges

Multiple distributed applications and security requirements

Multiple execution environments fragmented across platforms

Execution environments (EEs): transparency, security, interoperability limitations

#### **Transparency**

- Isolating enclave sensitive state

- Enclave size limitations

#### Security

Many side channel attacks

**Side-channels mitigation** orange for decentralized clouds

#### Interoperability

- Vendor lock-in

- OS functionality requirements

A non-uniform level of trust

**Single-TEE** industrial technologies

**AMD SEV**

arm **TRUSTZONE**

Have also security flaws

Multi-TEE "softwarized" technologies are highly promising

Lift hardware barriers

Microsoft

Enarx

OpenEnclave Asvlo

Extend also to the edge

Microsoft Graviton

Interoperability is still lacking but starting

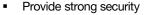

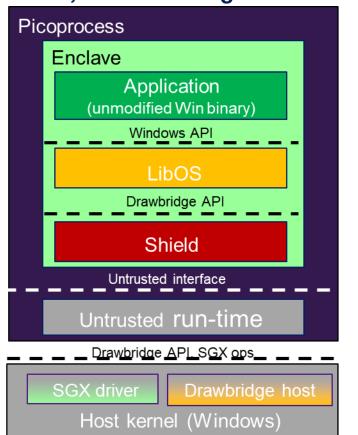

# legacy compatibility

Haven: private execution of unmodified binaries, mutual host-guest distrust

# Sandboxing: host vs. malicious guest

- Pico-process: secure isolation container

- Drawbridge LibOS:

- Narrow set of OS services

- Virtual memory, threading, I/O

- Support unmodified Windows binaries

# legacy compatibility

Haven: private execution of unmodified binaries, mutual host-guest distrust

# **Shielded execution:** applications vs. from untrusted host

#### Contain untrusted host OS

- LibOS: reduce attack surface

- Shield: reduce interface

- Validate untrusted inputs

- Encrypt / integrity protect private data Private scheduler

#### **Unmodified binary support**

- **Exceptions:**

- Emulate instruction behavior

- Page faults exposed to host OS

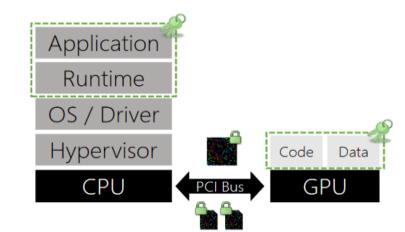

## co-processors

- TEE on GPUs: Graviton

- Confidentiality and integrity of computation and data

- Secure GPU/CPU interface

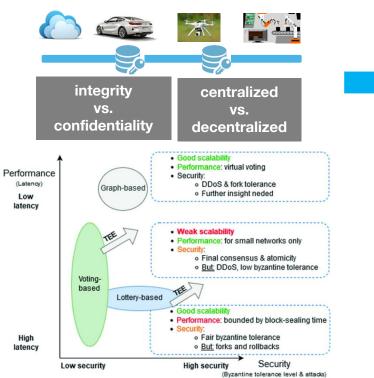

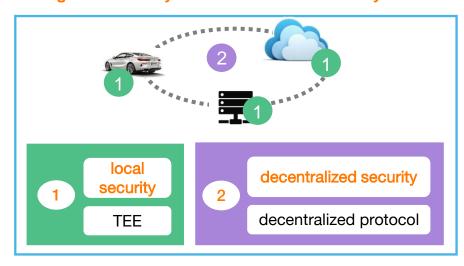

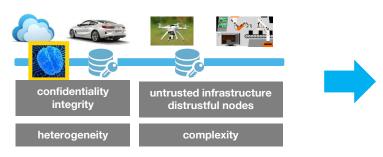

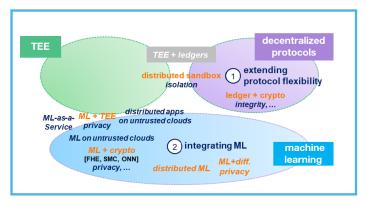

# decentralized protection of data

Future large-scale distributed applications have multiple data protection challenges

Network of TEEs architectures combine strong local security with decentralized security

#### Some remaining challenges

- Guarantee security of coupling between TEE and protocol

- Reach flexibility in protection architecture

#### extending decentralized flexibility to privacy-preserving Artificial Intelligence

# Apps perform distributed computations for automated predictions over private data

#### A rich landscape of hybrid solutions

#### Extend flexibility to integrate predictions

#### Beyond P2P solutions...

- Towards a <u>unified and open reference architecture</u> to orchestrate the different enablers

- The <u>open source approach</u> is promising to federate ecosystems

#### Some remaining challenges

- the previous heterogeneity challenges are magnified

- going towards a fully zero-trust model

## conclusion

- Vehicular systems: acute security & safety challenges for distributed isolation & trust

- Trusted computing approaches: strong guarantees by shielding applications

- Some challenges ahead:

- Distribution: Device, edge, cloud continuum Seamless mobility?

- Composition of security technologies

- Distributed/federated machine learning

- Heterogeneous processor architectures

- Latency requirements

- Side-channels

- Chains of Trust and certification

# Thank you

Marc Lacoste

Orange Innovation

Senior Research Scientist

marc.lacoste@orange.com